在DesignCon 2020大会上,ANSYS举办了一系列赞助演讲。我参加了其中的几场。这些活动都是由才华横溢、精力充沛的演讲者用他们的材料进行精彩的展示。DesignCon技术方案具有超前的纬度。其中一个是由乔治亚理工学院电子与计算机工程学院的Sung-Kyu Lim教授提出的——这个演示涉及到3D集成电路。

Lim教授的研究由DARPA、Arm和ANSYS资助。该讨论集中在用Arm A7和A53处理器构建的3D集成电路的热分析、IR-drop和PPA分析上。因为3D IC可以代表很多东西,所以Lim教授的重点是光模堆积。他用这些技术审查了来自GLOBALFOUNDRIES、英特尔(Intel)和台积电(TSMC)等公司的几项设计。

首先,简单介绍一下用于这些测试用例的设计流程。Lim教授在这里采取了一种实用的方法,将商业上可用的2D IC设计工具应用于3D设计问题上。逻辑/内存设计被分解成两层,一层用于逻辑,另一层用于内存。首先,内存层被设计一个引脚分配层。然后创建了一个双金属堆栈。这允许内存层和逻辑层通过使用硅穿孔TSV、面对面焊盘或单片层间通孔(MIV)通过密集连接进行通信。接下来,逻辑层与来自内存层的连接一起被放置和路由,这些连接也表示在逻辑层中。

该方法的结果讨论了一个Arm Cortex A7设计,包含L1, L2高速缓存和逻辑层。所有的L2和部分L1缓存被放置在内存层,其余的设计在逻辑层实现。因此,缓存和逻辑之间的互连缩短了很多。类似的过程也应用于Cortex A53的设计上。

由于采用了两层方法,这些实验的结果占用的空间更小,而且由于路线更短,性能得到了改善。但反过来,由于更快的运行速度导致了更大的功率,更高的红外下降和增加的温度,

此外,他们还进行了节能实验。本例采用LDPC纠错电路。由于更短的电线长度和更小的电容器,这节省了39%的电能,这说明了3D设计的另一个优点。

回到Arm的设计,下面是2D和3D之间各种实验的热图,进行热比较。

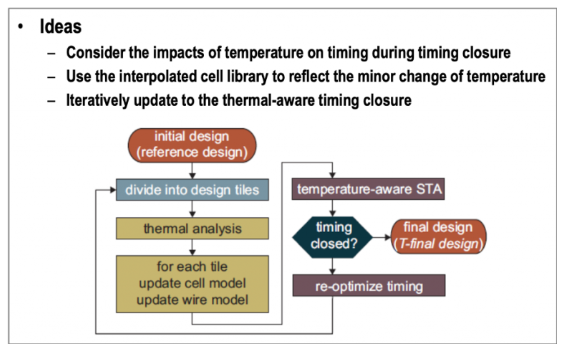

然后,Lim教授讨论了用于这些分析的工具流。其中说到被广泛用于执行许多任务的ANSYS RedHawk,包括功率,热和红外落差分析。所有这些工作都是基于对跨多个温度配置文件的每个路由段和设备的细粒度分析。下图是流程的概述。

在演讲的最后,Lim教授还讨论了热感知对集成电路设计的影响。他提出了一种温度感知的定时闭合流,可以根据实际的温度梯度来更新电路性能。这种方法可以产生在真实环境中更加有利的设计。

延伸阅读——Ansys RedHawk

芯片封装协同分析

在针对移动手机或服务器的电子系统中,处理器和存储器等 IC 负责执行应用程序和数据处理功能,消耗的功率最多。这些 IC 与它们的 I/O 电路之间输入/输出的数据量最大,并且产生的有害功率、热量以及 EMI 信号也最大。

IC 消耗的功率与其电源电压直接相关。由于阈值电压不会一同缩放,电源和阈值电压之间的差距缩小,从而降低了噪音容限。

随着技术的发展,由于封装阻抗日益增加,对降低成本和能耗的需求使芯片和封装级别的供电网络 (PDN) 设计变得复杂。这减少了电压,对芯片而言成为有害级别。

RedHawk-CPA 支持您无缝导入封装布局,以及针对封装感知和精确的片上静态 IR 以及交流热点分析考虑去耦电容和电感。

热感知 EM

ESD 及电源/接地和信号 EM 是亚 16nm 级别最迫切需要解决的两个可靠性问题。EM 和 ESD 分析的精确度以及覆盖率极为重要。随着导线中的电流增加,工作电压会降低,EM 范围会缩小。由于 FinFET 的使用,自热被添加到热问题中。在汽车等众多应用领域,了解、分析并优化每个 IC 设计以便实现正确热行为至关重要。

RedHawk 为热感知电源/接地和信号线 EM 验证提供全面支持,在尽量减少误报的同时准确分析 EM 冲突,即使是基于 FinFET 的先进设计亦可从中受益。在与 Ansys PathFinder 结合使用时,RedHawk 可以执行 SoC 级别 ESD 完整性分析,从 ESD 事件(HBM、CDM)为所有电流通路(导线和过孔)提供连接性和互连故障检查。RedHawk 在电源 EM、信号 EM 和 SoC ESD 签核方面获得芯片代工厂认证。

功能和容量

目前的片上系统 (SoC) 拥有更大规模的整合内容,并且采用先进的工艺技术。因此,必须考虑的设计参数的数量正在迅速增加。这为执行分析带来了性能瓶颈:最好的情况是要运行数天,最坏的情况是根本无法运行。

RedHawk 采用先进的分布式机器处理 (DMP) 技术,可为您提供模拟包含超10 亿个实例的设计所需的大容量和高性能。DMP 拥有的签核精确度仅可通过扁平仿真获得。

DMP 还利用私有机器群集不断增强的处理能力和可用存储容量,对整个芯片的 RLC 网络矩阵进行仿真,并使用完全分布式和交叉耦合的封装模型。通过执行全芯片扁平分析,RedHawk 能够保持动态降压、EM 和 ESD 的签核精确度。

经过硅验证的签核精确度

在芯片级别,对最新工艺技术的使用往往受到以下一个或多个因素的驱动:更快的性能、更大的带宽、更高的性能功率比和更小的晶片尺寸。工艺技术越新,失败的几率越大,设计错误造成的代价也就越高。这便是签核认证如此重要的原因。

自 2006 年以来,Ansys 工程师便在每个工艺技术方面与领先的晶圆代工厂展开紧密合作,确保 Ansys 解决方案考虑到工艺的所有新规则、参数和要求,并确保其结果与测试芯片的参考结果保持一致。

Ansys 多物理场解决方案经过所有主要晶圆代工厂的所有进阶 FinFET 流程节点的验证,包括 TSMC 最近的 5nm 流程技术。晶圆代工厂认证包括针对自发热、热感应 EM 的提取、电源完整性和可靠性、信号电迁移 (信号 EM) 和热可靠性分析以及统计 EM 预算 (SEB) 分析。这些严格的认证对于保证一次通过的硅晶至关重要。

电源噪音对时序的影响

设计中的动态压降可能对时钟抖动、关键路径和时序产生影响。如今的设计拥有多个时钟和电源域,在签核前对时钟树的性能进行评估,识别并分析抖动、信号串扰和时序问题便非常重要。

RedHawk 的快速全芯片级时序影响分析可帮助您评估时钟树性能。此外,它还支持您对可能受抖动、信号串扰和时序问题影响的电路零部件进行识别。RedHawk 的 SPICE 精确签核仿真可帮助您识别时钟树、受影响的关键路径和电路时序的问题,并采取措施消除这些问题。

高级 IC 封装的完整性与可靠性

对包括片上系统 (SoC) 在内的集成电路 (IC) 设计师而言,有一个持续的策略,就是通过集成化和小型化,在增加性能和带宽的同时降低能耗和占用面积。

对于任何封装技术,完整性、可靠性和成本都是需要优化的三大主要因素。完整性因素涉及电源和信号噪音。可靠性涉及热、电迁移 (EM)、静电释放 (ESD)、电磁干扰 (EMI) 和热致结构应力问题。成本则涉及几乎所有应用,尤其是消费品和物联网 (IoT) 设备。在每种芯片的封装、电路板和系统的背景下优化和确保芯片(晶片级别)的完整性和可靠性,这非常复杂,并且涉及多个晶片时成本只会增加。

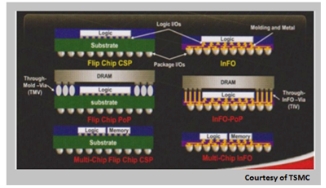

Ansys 解决方案使您能够确保您先进的 2.5D 或 3D-IC 封装设计可满足芯片、封装和系统级别的完整性和可靠性要求。Ansys 解决方案符合所有先进的 3D-IC 封装技术,包括 TSMC 最新的 CoWoS、InFO_MS 以及 SoIC 封装技术。Ansys 针对先进封装技术的多物理场解决方案能够进行多模具联合模拟和联合分析,实现提取、电源和信号集成分析、电源和信号电迁移分析、热量和热导压力分析。

什么是TSV封装?

3D IC技术蓬勃发展的背后推动力来自消费市场采用越来越复杂的互连技术连接硅片和晶圆。这些晶圆包含线宽越来越窄的芯片。

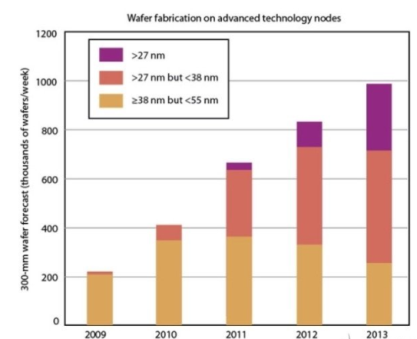

为了按比例缩小半导体IC,需要在300mm的晶圆上生成更精细的线条。据市场研究机构VLSI Research预测,虽然目前大多数量产的IC是基于55nm或55nm以下的设计节点,但这些设计规则将缩小至38nm或更小,到2013年甚至会缩小到27nm。

硅通孔技术(Through Silicon Via, TSV)技术是一项高密度封装技术,正在逐渐取代目前工艺比较成熟的引线键合技术,被认为是第四代封装技术。TSV技术通过铜、钨、多晶硅等导电物质的填充,实现硅通孔的垂直电气互连。硅通孔技术可以通过垂直互连减小互联长度,减小信号延迟,降低电容/电感,实现芯片间的低功耗,高速通讯,增加宽带和实现器件集成的小型化。基于TSV技术的3D封装主要有以下几个方面优势:

1)更好的电气互连性能,

2)更宽的带宽,

3)更高的互连密度,

4)更低的功耗,

5)更小的尺寸,

6)更轻的质量。

TSV工艺主要包括深硅刻蚀形成微孔,绝缘层/阻挡层/种子层的沉积,深孔填充,化学机械抛光,减薄、pad的制备及再分布线制备等工艺技术。主要工艺包括几个部分:

(1)通孔的形成;

(2)绝缘层、阻挡层和种子层的淀积;

(3)铜的填充(电镀)、去除和再分布引线(RDL)电镀;

(4)晶圆减薄;

(5)晶圆/芯片对准、键合与切片。

TSV深孔填充技术是3D集成的关键技术,也是难度较大的一个环节,TSV填充效果直接关系到集成技术的可靠性和良率等问题,而高的可靠性和良率对于3D TSV 堆叠集成实用化是至关重要的。另外一个方面为在基片减薄过程中保持良好的完整性,避免裂纹扩展是TSV工艺过程中的另一个难点。

TSV技术本质上并不是一种封装技术方案,而只是一种重要的工具,它允许半导体裸片和晶圆以较高的密度互连在一起。基于这个原因,TSV在大型IC封装领域中是一个重要的步骤。但TSV不是推动3D封装技术进步的唯一方法。它们仅代表众多材料、工艺和封装开发的一个部分。

未来的3D堆栈可能包含处理器、存储器、逻辑和模拟及RF电路,所有这些都通过TVS互连。流体通过MEMS微通道实现冷却。